电路元器件的降额设计

一、电路设计为何需要元器件降额?

不知你是否发现过电路中常存在的这些情形:5V的工作电压却选用16V额定电压的电解电容,电路上的电阻功率使用比理论计算值大几倍、几十倍等等,这些情形都是电路的元器件降额设计。

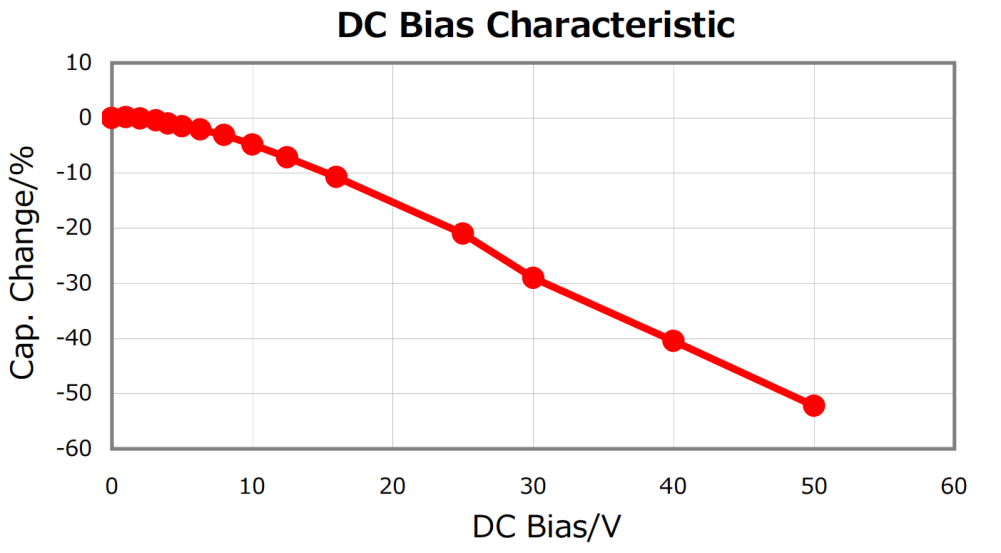

有这样一组可靠性试验,同样的铝电解电容在不同的工作电压下的失效试验,一个施加100%工作电压,测量电容顶部外壳温度为80度,一个施加40%工作电压,其电容顶部外壳同样位置温度为40度;一般已知,如果使用温度升高10℃,产品的寿命就会减少1/2,即“10℃下降2倍定律”。百特公司产品主要运用于工业场合,环境温度可达-20~60度,对于产品自身的温升需要有更加严格的要求,元器件更应进行降额处理,否则可靠性和寿命会大大降低。另外一种情况,元件器在真实运用中它的参数是什么?比如常见的贴片陶瓷电容104/50V,材质X7R,它的直流偏置电压特性如图1所示,随着工作电压上升,其电容量会下降,在50V时下降到50%,电容值从100nF变成50nF,它如果工作在50V就会与预期的设计值相差过大。

图1

降额设计除参考各元件器厂家的参数数据资料,还可遵循国家标准,国军标《GJBZ35-93军用标准元器件降额准则》,航空标准《QJ1417-1988 元器件可靠性降额准则》。降额作为提升产品可靠性的基础手段,已经被业界广泛采用,理解和应用降额首先需要先了解相关基本术语。

降额(derating):元器件承受的应力低于其额定值,以达到延缓其参数退化,提高元器件可靠性,通常用应力比和环境温度来表示。

额定值(rating):元器件允许的最大使用应力值。

应力(stress):影响元器件失效的电、热、机械等负载。

应力比 (stress ratio):元器件工作应力与额定应力之比,又称降额因子。

I级降额:最大的降额,元器件使用可靠性的改善最大。

II级降额:元器件使用可靠性有明显改善。

III级降额:元器件使用可靠性的相对效益最大,改善效果不如I级和II级降额但最易实现。

二、如何理解降额

电子元件器都是由各种物理材料构成,存在一个或多个极限特性。降额就是将元件器的材料固有特性(电、热、机械等应力)降低使用,比如一段绳子可以承受100N的最大拉力,但却选用70N拉力使用,避免瞬间拉力过大造成绳子崩断,这就是一种通俗的降额思想。

真实世界的电子元器件的应力来源还有供应商、制造过程、生产批次、仓库存储、物流运输等,提高降额等级是应对这些不确定性,增加产品可靠性的基础办法。比如在回流焊高温的制造过程中,元器件本身不是单一材料,PCB板材又是另一种材料,它们内部热分布不均匀,材料的膨胀系数也不同,制造过程会加剧元器件应力问题。

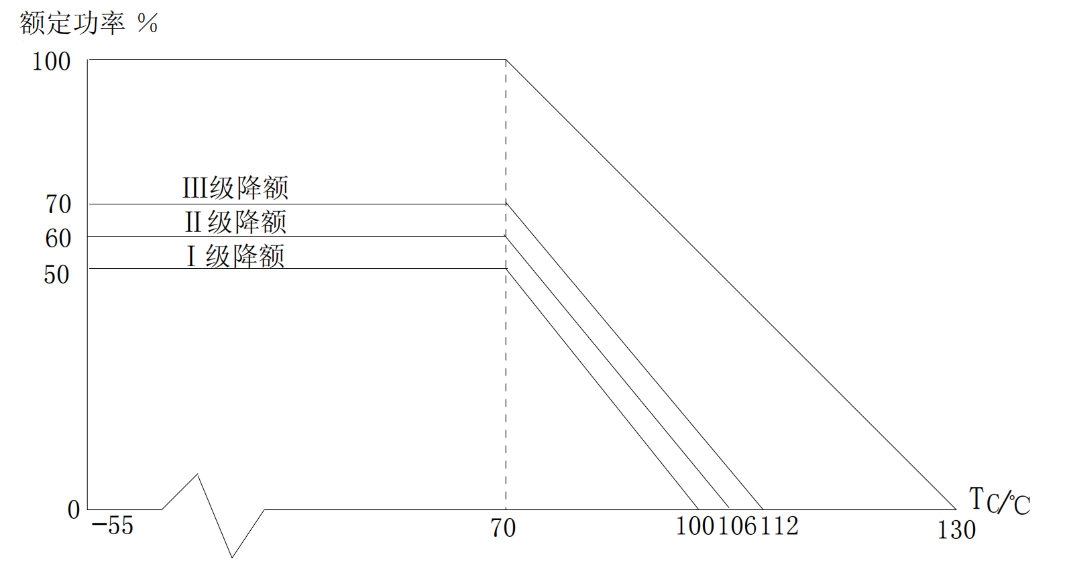

降额设计除了根据长期的工程实践经验,还可以参考《GJBZ35-93军用标准元器件降额准则》,标准内有相应的降额参数、降额曲线图,只要将设计落入相应降额等级范围内即可实现降额,如电阻降额曲线图2。

图2

三、常用元器件的降额方法

1、电阻降额

GJBZ35-93标准里的薄膜型电阻降额准则如表1所示。

降额参数 | 降额 | ||

I | II | III | |

电压 | 0.75 | 0.75 | 0.75 |

功率 | 0.5 | 0.6 | 0.7 |

环境温度 | 按元件负荷特性曲线降额 | ||

表1

公司产品常用的贴片电阻0603型功率1/10W,最大工作电压50V;0805型功率1/8W,最大工作电压150V,工作电压都可满足降额条件。如果按I级降额设计,5V工作电压,0603不能超过10mA工作电流,0805不能超过12.5mA工作电流。对于端口保护电阻,可使用1206封装,最高工作电压200V,提高降额等级,对于高精度采样电阻也应提高降额等级降低温漂对精度影响。

2、电容降额

标准里的固定陶瓷电容降额准则如表2所示。

降额参数 | 降额 | ||

I | II | III | |

直流工作电压 | 0.5 | 0.6 | 0.7 |

环境温度 | TAM-10 (TAM元件最高环境温度) | ||

表2

公司产品常用贴片电容(MLCC)0603型、0805型额定电压50V,大于I级降额条件,X7R与C0G 材质温度特性-55~125℃,X5R材料-55~85℃,都可满足降额参数。

标准里的电解电容降额准则如表3所示。

降额参数 | 降额 | |||

I | II | III | ||

铝电解 | 直流工作电压 | - | - | 0.75 |

环境温度 | - | - | TAM-20 | |

钽电解 | 直流工作电压 | 0.5 | 0.6 | 0.7 |

环境温度 | TAM-20 | |||

表3

铝电解电容不能承受低温度和低气压,只限于地面使用。工作电压3V或5V时,公司常用的铝电解电容与钽电容额定电压为16V,高于I级降额条件,其它的更高工作电压,宜根据设计需求与成本考虑选择恰当的电解电容。

3、集成电路降额

集成电路种类繁多,它们内部的电路单元很小,在导体断面上的电流密度大,可能存在高温有源结点,高结温是集成电路的最大破坏应力,芯片降额主要手段是降低芯片结温。可以从电压、电流、功率、结温这些参数来降低结温。标准里的模拟集成电路降额准则如表4所示。

降额 参数 | 放大器 | 比较器 | 电压调整器 | 模拟开关 | ||||||||

降额等级 | 降额等级 | 降额等级 | 降额等级 | |||||||||

I | II | III | I | II | III | I | II | III | I | II | III | |

电源 电压 | 0.7 | 0.8 | 0.8 | 0.7 | 0.8 | 0.8 | 0.7 | 0.8 | 0.8 | 0.7 | 0.8 | 0.85 |

输入 电压 | 0.6 | 0.7 | 0.7 | 0.7 | 0.8 | 0.8 | 0.7 | 0.8 | 0.8 | 0.8 | 0.85 | 0.9 |

输入输出电压差 | - | - | - | - | - | - | 0.7 | 0.8 | 0.85 | - | - | - |

输出 电流 | 0.7 | 0.8 | 0.8 | 0.7 | 0.8 | 0.8 | 0.7 | 0.75 | 0.8 | 0.75 | 0.8 | 0.85 |

功率 | 0.7 | 0.75 | 0.8 | 0.7 | 0.75 | 0.8 | 0.7 | 0.75 | 0.8 | 0.7 | 0.75 | 0.8 |

最高 结温 | 80 | 95 | 105 | 80 | 95 | 105 | 80 | 95 | 105 | 80 | 95 | 105 |

表4

以集成电路芯片器件手册的绝对最大工作等级为参数,计算上述表格的降额条件,即可知道芯片是否符合降额要求。结温的降额应该使用相应的热设计,增加导热散热,用测温枪测量实物电路的温度分布情况然后调整设计。

四、总结

电路元器件降额是一个在电路设计、电子工程实践中重要且不可忽视的观念。在实际应用中,我们需要充分认识到各种元器件性能可能发生降低的情况并了解其特点,通过合理选择元件、优化设计和实施有效措施,才可以最大程度增强电子产品稳定性和性能。